Cache Coherence - GeeksforGeeks

Jul 15, 2025 · As multiple processors operate in parallel, and independently multiple caches may possess different copies of the same memory block, this creates a cache coherence problem.

Cache Coherence Problem and Approaches - Medium

Mar 23, 2019 · The Cache Coherence Problem is the challenge of keeping multiple local caches synchronized when one of the processors updates its local copy of data which is shared among …

Cache coherence - Wikipedia

Without cache coherence, a change made to the region by one client may not be seen by others, and errors can result when the data used by different clients is mismatched.

Cache coherence problem exists because there is both global storage (main memory) and per-processor local storage (processor caches) implementing the abstraction of a single shared address …

Memory coherence problem exists because there is both global storage (main memory) and per-processor local storage (processor caches) implementing the abstraction of a single shared address …

Cache Coherence and Synchronization - Online Tutorials Library

As multiple processors operate in parallel, and independently multiple caches may possess different copies of the same memory block, this creates cache coherence problem.

What is Cache Coherence? Problem & Protocols -Binary Terms

In this section, we will discuss the cache coherence problem and the protocol for resolving the cache coherence problem. What is Cache Coherence Problem? In a multiprocessor environment, all the …

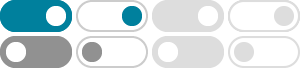

More scalable solution: ‘directory based’ coherence schemes Snooping Protocols Write Invalidate CPU wanting to write to an address, grabs a bus cycle and sends a ‘write invalidate’ message All …

- [PDF]

14_consistency

The cache coherency problem exists because hardware implements the optimization of duplicating data in multiple processor caches. The copies of the data must be kept coherent.

14.5. Cache Coherence and False Sharing - Dive Into Systems

A cache coherence strategy invalidates or updates cached copies of shared values in other caches when a write to the shared data value is made in one cache. The Modified Shared Invalid (MSI) …